| ID |

Date |

Author |

Status |

Type |

Category |

Important |

Subject |

Icon |

|

38

|

Mon Mar 7 14:49:27 2022 |

Entered by Nicolas Delerue from 134.158.195.144 on Mon Mar 7 14:49:13 2022 | Under Process | Problem | Material |

|

Probleme ecran Synthe linac | |

L 'ecran du synthe linac ne fonctionne plus.

Il est possible de se connecter au synthe linac par telnet avec la commande suivante:

$ telnet synthe-b8 5025

Ensuite envoyer les commandes du manuel chapitre 7 page pdf 389.

|

|

37

|

Thu Mar 3 13:23:22 2022 |

Entered by Vincent Chaumat from 134.158.88.158 on Thu Mar 3 13:23:06 2022 | Fixed | Info | Other |

|

Phase relative oscillateur laser/3GHz | |

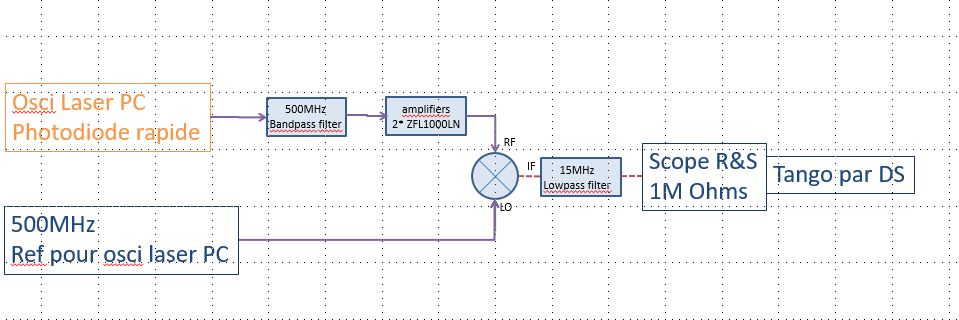

Sensibilité en Phase du systeme de mesure temps réel de la phase relative entre l'oscillateur laser PC et le 500MHz

1 °3GHz/mV la précision de la mesure est de 1.5 °3GHz eff

Schéma de la mesure :

en attaché

A travers le déphaseur intégré dans l’oscillateur on fait varier la valeur de la phase (en pas 0 à 17000)

La valeur de la tension est mesurée à l’oscilloscope (impédance 1MOhms) (data en attaché)

Un fit est réalisé (matlab) pour obtenir la pente : 364mV/rad. A 500MHz la sensibilité en temps est de 318ps/rad.

On a donc une sensibilité (autours du zéro en sortie du mélangeur) de 0.87ps/mV

Soit à 3GHz une sensibilité de l’ordre de 1 °3GHz/mV la précision de la mesure est de 1.5 °3GHz eff

|

Step dephaseur oscillateur (nB)

|

Sortie mélangeur (mV)

|

|

0

|

69

|

|

500

|

2,1

|

|

1000

|

-76

|

|

1500

|

-143

|

|

2000

|

-180

|

|

2500

|

-229

|

|

3000

|

-292

|

|

3500

|

-345

|

|

4000

|

-370

|

|

4500

|

-390

|

|

5000

|

-378

|

|

5500

|

-337

|

|

6000

|

-304

|

|

6500

|

-259

|

|

7000

|

-178

|

|

7500

|

-103

|

|

8000

|

-57

|

|

8500

|

-10

|

|

9000

|

61

|

|

9500

|

129

|

|

10000

|

170

|

|

10500

|

208

|

|

11000

|

272

|

|

11500

|

331

|

|

12000

|

339

|

|

12500

|

378

|

|

13000

|

380

|

|

13500

|

363

|

|

14000

|

335

|

|

14500

|

309

|

|

15000

|

248

|

|

15500

|

167

|

|

16000

|

102

|

|

16500

|

57

|

|

17000

|

-16

|

|

| Attachment 1: mesure_phase_500MHz_oscillateurlaserPC.xlsx

|

| Attachment 2: schéma_mesure.JPG

|

|

|

36

|

Tue Mar 1 16:58:35 2022 |

Entered by Vincent Chaumat from 134.158.88.158 on Tue Mar 1 16:58:19 2022 | Fixed | Fix | Timing |

|

Signaux de déclenchement | |

Aujourd'hui, François et moi avons mis à jour le firmware de la CPLD du systeme de génération des voies de déclenchement. Les "coups manqués" ont disparu, 3 pendant pendant 6 H de fonctionnement (environ 1 tous les 10s avant) |

|

35

|

Mon Feb 14 10:15:26 2022 |

Entered by Moutardier Alexandre from 134.158.195.142 on Mon Feb 14 10:15:13 2022 | Under Process | Fix | Timing |

|

Recette synchro | |

Recette du 01-02-2022 rechargé et sauvé sous le nom : 20220201_reference.xml

Correction d'un bug de lecture de recette dans le script => git push nécésaire pour pouvoir recharger une recette ! |

|

34

|

Fri Feb 11 11:29:48 2022 |

Entered by SC/HM/VS from 134.158.195.141 on Fri Feb 11 11:10:04 2022 | Under Process | Problem | Other |

|

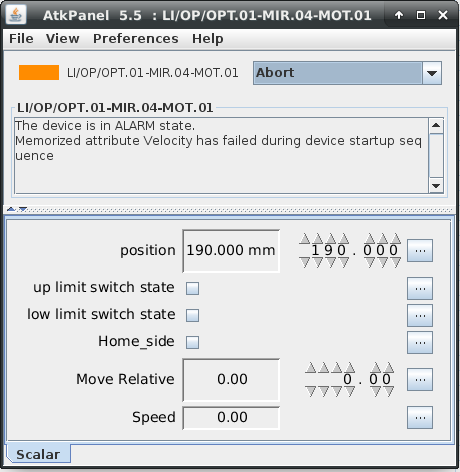

DS miroirs lasers M4 et M5 | |

Impossible d'accéder au DS des miroirs M4 et M5 du laser.

Impossible d'aligner le laser sans les miroirs.

|

| Attachment 1: Screenshot_2022-02-11_11-29-03.png

|

|

|

33

|

Fri Feb 4 15:35:49 2022 |

Entered by Moutardier Alexandre from 134.158.195.142 on Fri Feb 4 15:35:36 2022 | | Info | Tests |

|

Test AcqAttrManager | |

DS AcqAttr mannager démarrer correctement.

Générateur de retard Diag : Voies T6, T7, T8 (WAC) mise en SSE

-> Tir sigle shot sur le géné nécéssaire au début

Sinon cela fonctionne.

Retour en config normal. |

|

32

|

Fri Feb 4 15:25:47 2022 |

Entered by Nicolas Delerue from 134.158.195.144 on Fri Feb 4 15:25:32 2022 | Fixed | Fix | Timing |

|

Trigger RDPY etait sur SSE | |

Le trigger de la voie 14 du generateur 3 (diags) qui correspond a une redpitya etait sur SSE (tir unique). Il a ete remis sur EXT (mode normal avec declenchement externe). |

|

31

|

Fri Jan 14 11:05:12 2022 |

Entered by Super Team from 134.158.195.141 on Fri Jan 14 10:44:08 2022 | Fixed | Question | Timing |

|

RE: Démarrage des DS des générateurs de retard | |

MAUVAIS REPERTOIR !!!

Pour lancher les 2 DS il faut faire :

cd /data/shared/tangoscripts/DeviceServer/DS_CALC/Synchro/

./launch_ds_gene_retard_loc.sh

AM

| Entered by Super Team from 134.158.195.141 on Fri Jan 14 10:44:08 2022 wrote: |

|

Pour redémarrer le DS Sim.SY/DEG.sim :

/data/shared/DS_CALC/launch_ds_gene_retard.sh &

(Comment démarrer Sim.SY/DEG2.sim ?)

|

|

|

30

|

Fri Jan 14 10:44:21 2022 |

Entered by Super Team from 134.158.195.141 on Fri Jan 14 10:44:08 2022 | Under Process | Question | Timing |

|

Démarrage des DS des générateurs de retard | |

Pour redémarrer le DS Sim.SY/DEG.sim :

/data/shared/DS_CALC/launch_ds_gene_retard.sh &

(Comment démarrer Sim.SY/DEG2.sim ?) |

|

29

|

Tue Jan 4 15:26:52 2022 |

Entered by Nicolas Delerue from 80.119.21.73 on Tue Jan 4 15:26:37 2022 | Fixed | Problem | Timing |

|

Tous les DEG avaient été réinitialisés... | |

Tous les DEG avaient été remis à zéro... Peut-être qu'une interface synchro était ouverte au moment où le DS a été rechargé?

J'ai remis la config 6.

J'ai vérifié les largeurs de:

GENERATOR_2_CHANNEL_1: 'Ring pulsed injection' => 320ns

GENERATOR_2_CHANNEL_2: 'Ring pulsed extraction' => 320ns

GENERATOR_2_CHANNEL_3: 'Ring pulsed septum' => 5000ns

|

|

28

|

Mon Jan 3 17:14:09 2022 |

Entered by Nicolas Delerue from 134.158.195.142 on Mon Jan 3 17:00:57 2022 | Fixed | Fix | Material |

|

RE: Synchro redemarree | |

Declenchement OK

| Entered by Nicolas Delerue from 134.158.195.142 on Mon Jan 3 17:00:57 2022 wrote: |

|

La synchro a ete redemaree avec les reglages de la memoire 6.

|

|

|

27

|

Mon Jan 3 17:01:11 2022 |

Entered by Nicolas Delerue from 134.158.195.142 on Mon Jan 3 17:00:57 2022 | Fixed | Fix | Material |

|

Synchro redemarree | |

La synchro a ete redemaree avec les reglages de la memoire 6. |

|

26

|

Fri Dec 17 20:26:27 2021 |

Entered by Nicolas Delerue from 80.119.21.73 on Fri Dec 17 20:26:12 2021 | Under Process | Info | Timing |

|

Synchro éteinte | |

Bonjour,

En prévisions de la coupure électrique, la synchro côté linac a été éteinte. La synchro côté anneau était déjà éteinte quand je suis arrivé. |

|

25

|

Mon Dec 13 17:53:10 2021 |

Entered by Nicolas Delerue from 80.119.21.73 on Mon Dec 13 17:52:57 2021 | Under Process | Fix | Timing |

|

Intervention IHM retards déclenchement | |

Les réglages actuels des retards sont sauvés dans la mémoire 6.

Le code de cron_synchro.py a été modifié de manière à prendre la valeur OVERALL_DELAY dans synchro_constants et à la retirer de la valeur lue dans le DEG lorsque celle-ci est écrite dans Tango. Inversement cette valeur est ajouté à la valeur TANGO lorsqu'elle est écrite dans le DEG.

Une bibliothèque synchro_tools.py a été écrite afin de permettre des balayages en temps.

|

|

24

|

Wed Nov 3 08:08:21 2021 |

Entered by vincent.chaumat from 134.158.88.158 on Wed Nov 3 08:00:30 2021 | Not Fixed | Problem | Timing |

|

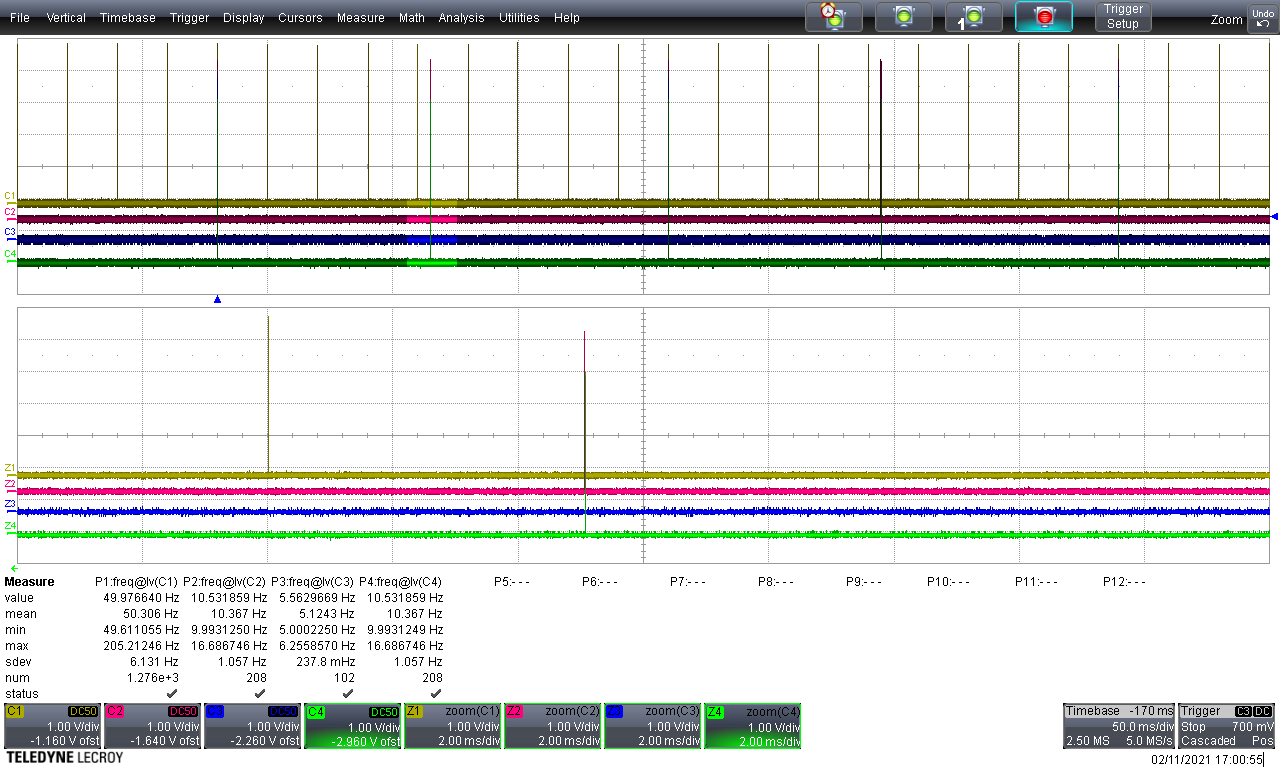

Carte synchro CPLD, entered from 134.158.88.158 | |

La carte synchro CPLD du chassis synchro a les sorties DEG 2 3 4 qui se décale par rapport à la sortie DEG1 (50 Hz) avec un taux de répétition aléatoire. Le Décalage temporel est constant (5ms) entre les front montant DEG1 et DEG 2 3 4.

voir la prise d'écran ci dessous: partie haute acquisition (jaune deg1 rouge deg 2 bleu deg3 vert deg4) la partie basse est le zoom de la partie haute (surbrillance)

|

| Attachment 1: erreur_timing1.png

|

|

|

23

|

Tue Nov 2 16:19:42 2021 |

Entered by vincent.chaumat from 134.158.195.144 on Tue Nov 2 16:19:18 2021 | Not Fixed | Problem | Timing |

|

DEG1 50Hz | |

NNous avons un pB qsur le DEG1 en salle de controle:

bien que ce soit la fréquence la plus élevée, il manque parfois des "coups" par rapport aux fréquences les plus basses Linac Diag...

cela explique les "tirs" ratés que l'on a parfois (pas de signal modulateur => pas de pulse HT

je ne sais pas à quel point cela peux faire disfonctionner le modulateur qui doit etre à 50Hz

le conditionnemt est en cours je ne peux pas investiguer plus

|

|

22

|

Fri Oct 29 10:48:11 2021 |

Entered by Moutardier Alexandre from 134.158.195.144 on Fri Oct 29 10:47:58 2021 | Fixed | Fix | Timing |

|

décalage de "seulement" 40µs | |

Suite a un oublis de sauvegarde de la configuration décalé de 100µs, et un redémarrage du ds sim, il a fallu refaire les décalage de retard.

Nicolas trouvant que 100µs était trop, j'ai cherché le minimum de retard possible pour avoir un signal sur la caméra linac.

Après quelque test, j'ai décallé les retard de 40µs et ça focnctionne pour la caméra linac et la caméra laser.

sauvé dans : 20211028_1105_deplacement_trigger_linac_a_40_micro_s.xml |

|

21

|

Wed Oct 27 17:18:38 2021 |

Entered by Super Team from 134.158.195.141 on Wed Oct 27 16:26:02 2021 | New Solution | Info | Timing |

|

RE: décalage délais | |

Impossible de passer à un trigg diag à plus de 1 HZ

| Entered by Super Team from 134.158.195.141 on Wed Oct 27 16:26:02 2021 wrote: |

|

Décalage de tous les délais de 40us effectué par Alexandre M.

Cela permet de trigger les caméras avec les ~ 70us d'avance. Caméras linac et photoCathode, réglées à 0 dans l'IHM des retard.

|

|

|

20

|

Wed Oct 27 16:26:14 2021 |

Entered by Super Team from 134.158.195.141 on Wed Oct 27 16:26:02 2021 | New Solution | Info | Timing |

|

décalage délais | |

Décalage de tous les délais de 100us effectué par Alexandre M.

Cela permet de trigger les caméras avec les ~ 70us d'avance. Caméras linac et photoCathode, réglées à 0 dans l'IHM des retard. |

|

19

|

Tue Oct 19 14:13:15 2021 |

Entered by vincent.chaumat from 134.158.195.144 on Tue Oct 19 14:12:56 2021 | Fixed | Problem | Timing |

|

frequence DG3 | |

La fréquence des signaux de déclenches du DG3 (diag ) est conforme à celle de l'IHM en salle de controle:

Une des voies (ch16) avait un retard supérieur à la période du 5Hz interdisant un fonctionnement correcte du générateur de retard.

Peut etre faudrait il limiter les retards et les largeurs (en soft) pour ne plus avoir ce genre de probleme

Vincent |