| ID |

Date |

Author |

Status |

Type |

Category |

Important |

Subject |

Icon |

|

118

|

Fri May 16 11:12:32 2025 |

Entered by Vincent Chaumat from 134.158.76.115 on Fri May 16 11:12:17 2025 | Fixed | Info | Timing |

|

State of the art Synchro | |

Les performance de la synchro de ThomX au 16 mai 2025 sont:

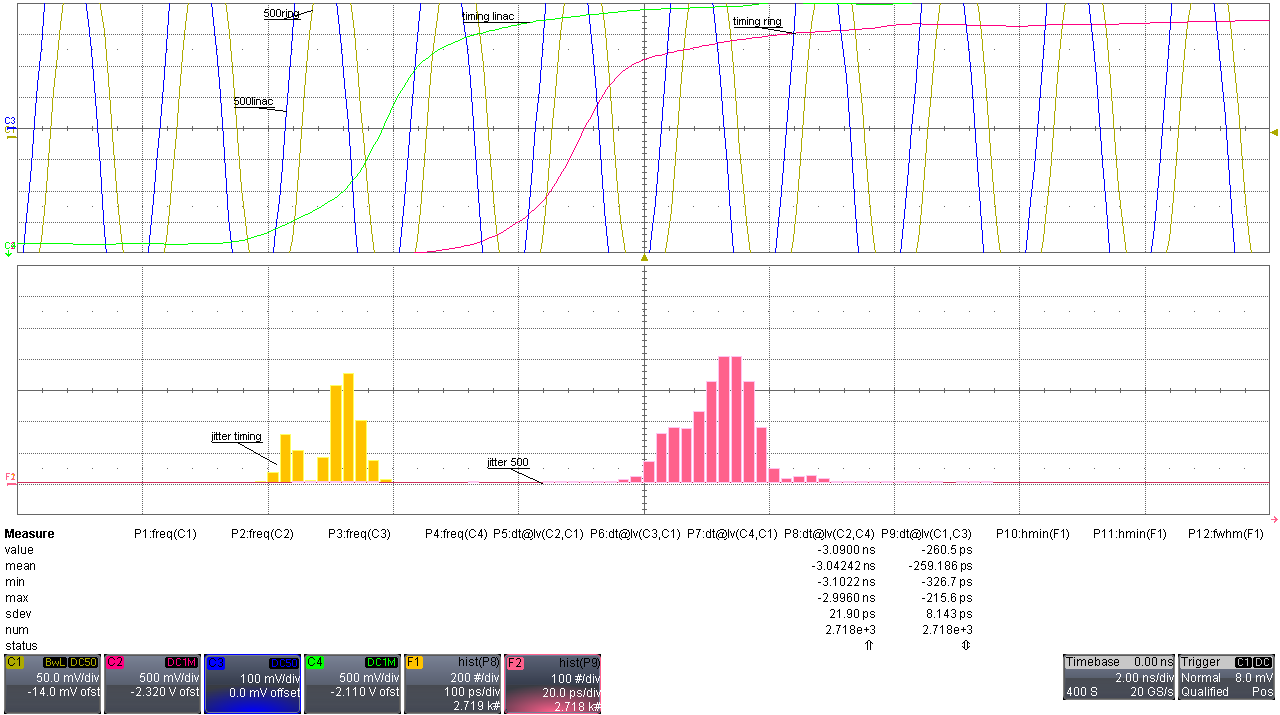

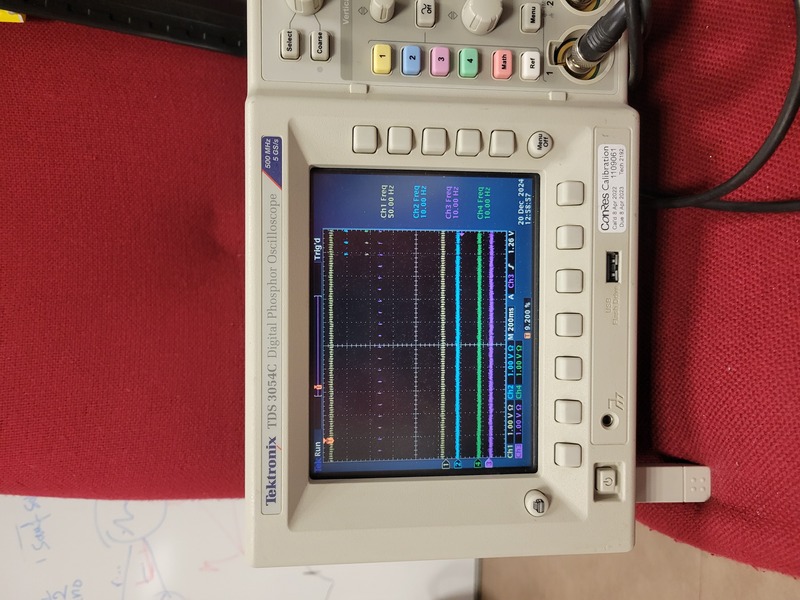

Le jitter 500MHz Ring 500MHz Linac est de 8ps Sdev et 95% es événement dans 20ps 100 % dans 80ps (quelquesoit la fréquence de répétion) (Jitter rapide)

Le jitter entre les voies de synchro Linac et Ring est contenu dans 100ps (quelquesoit la fréquence de répétion) (jitter rapide)

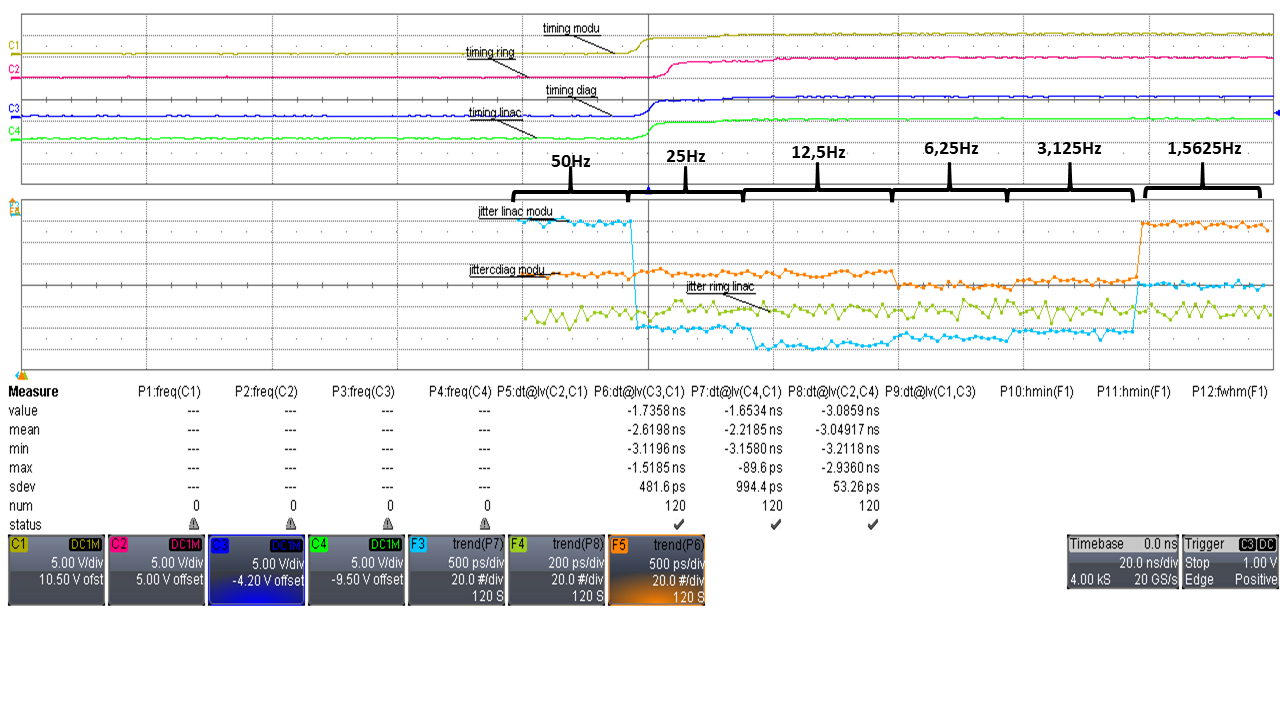

La varition du temps entre les timing ring (drift timing) (quelquesoit la fréquence de répétion)

sont inférieurs à 3ns entre le modulateur et le linac

sont inférieurs à 1.5ns entre le modulateur et les diag

sont inférieurs à 200ps entre linac et ring (mesure plus précise avec jitter rapide)

|

| Attachment 1: jitter_rapide.png

|

|

| Attachment 2: drift_timing.png

|

|

|

117

|

Tue May 13 16:04:37 2025 |

ND | Not Fixed | Problem | Other |

|

RE: RE: Rapport frequence anneau | |

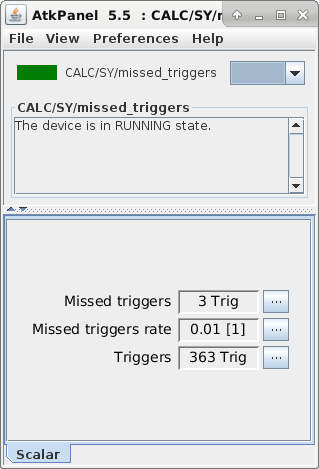

Rappel: pour voir le taux de declenchement manqués taper:

atkpanel CALC/SY/missed_triggers

| ND wrote: |

|

Rien dans les logs permettant d'identifier le problème.

J'ai utilisé ring_cavity pour changer la fréquence et le problème s'est résolu.

J'ai modifié la sortie de ./ring_frequency.py --read pour détecter les désaccords en fréquence...

| VC wrote: |

|

probleme de saute sunchro (50Hz)

avec le programme ./ring_frequency.py --read (les fréquence lues sont validées directement sur les générateurs anneaux)

('ring freq', '+5.0010045000000E+08\n', 500100450.0)

('Commande: ', ':SOURce2:Freq?')

('Commande: ', ':SOURce2:Freq?')

('data', '3.334002E+07\n')

('Commande: ', ':SOURce1:Freq?')

('Commande: ', ':SOURce1:Freq?')

('data', '3.334002E+07\n')

('sub freq', '3.334002E+07\n')

les deux fréquence ne sont pas multiples entière entre elles: 500.100450 /15 = 33.34003 ou 33.34005*15= 500.1003

Vincent

|

|

|

|

116

|

Tue May 13 12:32:18 2025 |

ND | Not Fixed | Problem | Other |

|

RE: Rapport frequence anneau | |

Rien dans les logs permettant d'identifier le problème.

J'ai utilisé ring_cavity pour changer la fréquence et le problème s'est résolu.

J'ai modifié la sortie de ./ring_frequency.py --read pour détecter les désaccords en fréquence...

| VC wrote: |

|

probleme de saute sunchro (50Hz)

avec le programme ./ring_frequency.py --read (les fréquence lues sont validées directement sur les générateurs anneaux)

('ring freq', '+5.0010045000000E+08\n', 500100450.0)

('Commande: ', ':SOURce2:Freq?')

('Commande: ', ':SOURce2:Freq?')

('data', '3.334002E+07\n')

('Commande: ', ':SOURce1:Freq?')

('Commande: ', ':SOURce1:Freq?')

('data', '3.334002E+07\n')

('sub freq', '3.334002E+07\n')

les deux fréquence ne sont pas multiples entière entre elles: 500.100450 /15 = 33.34003 ou 33.34005*15= 500.1003

Vincent

|

|

|

115

|

Tue May 13 11:11:24 2025 |

VC | Not Fixed | Problem | Other |

|

Rapport frequence anneau | |

probleme de saute sunchro (50Hz)

avec le programme ./ring_frequency.py --read (les fréquence lues sont validées directement sur les générateurs anneaux)

('ring freq', '+5.0010045000000E+08\n', 500100450.0)

('Commande: ', ':SOURce2:Freq?')

('Commande: ', ':SOURce2:Freq?')

('data', '3.334002E+07\n')

('Commande: ', ':SOURce1:Freq?')

('Commande: ', ':SOURce1:Freq?')

('data', '3.334002E+07\n')

('sub freq', '3.334002E+07\n')

les deux fréquence ne sont pas multiples entière entre elles: 500.100450 /15 = 33.34003 ou 33.34005*15= 500.1003

Vincent

|

|

114

|

Mon May 5 12:17:18 2025 |

VC, ND | | Info | Timing |

|

Mise a jour synchronisation. | |

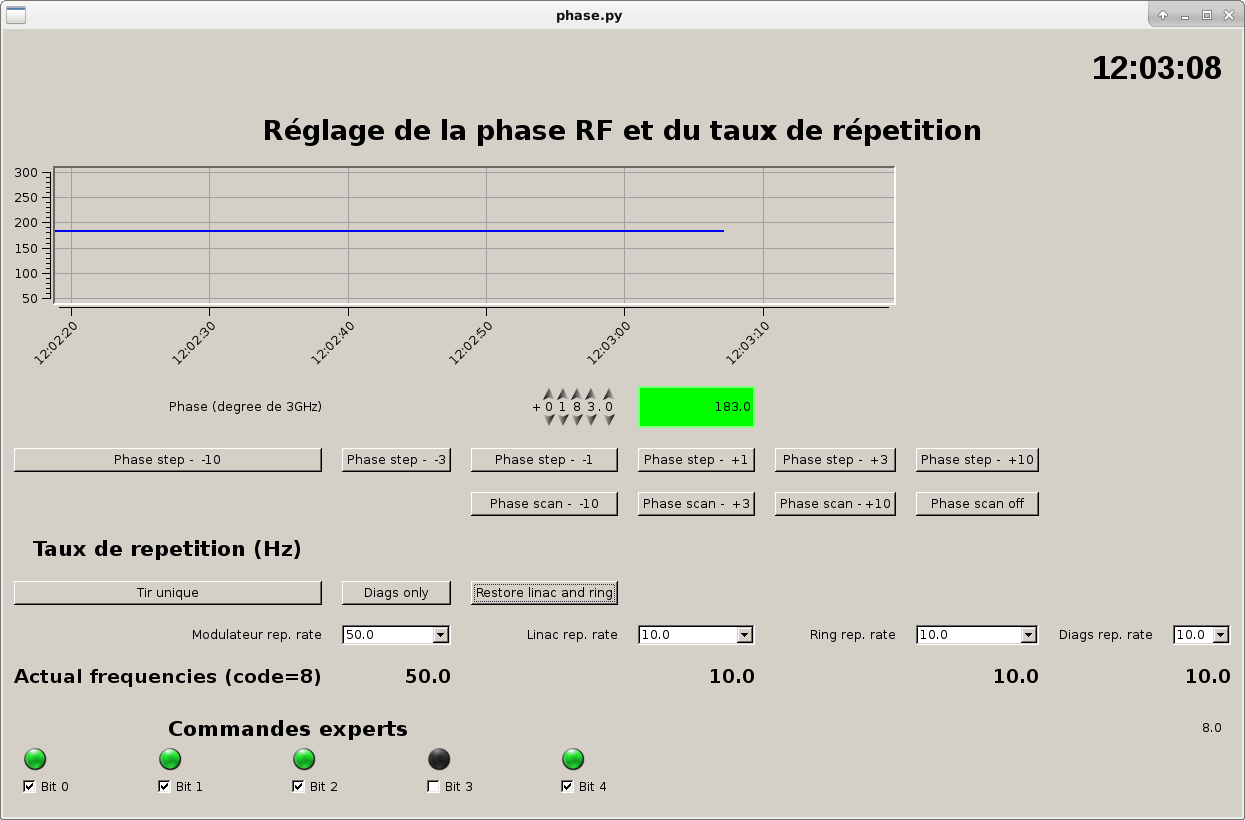

Attention au démarrage de l'interface faire 'restore laser and Kicker' pour etre sur que le systeme de synchro est en mode "normal"

Les codes de synchronisations ont ete mis a jour afin de permettre le 50Hz.

L'interface a ete mise à jour et un git pull a ete fait.

Le bit 4 est un reset du CPLD (il n'y a plus de synhcro tant que Bit 4 = 1 et la LED du chassis synchro ne clignote pas)

Il existe 6 codes possibles

Modulateur Linac Ring Diag

code 1 50 50 50 12.5

code 2 50 25 25 12.5

code 3 50 12.5 12.5 12.5

code 4 50 6.25 6.25 6.25

Code 5 50 3.125 3.125 3.125

Code 6 50 1.5625 1.5625 1.5625

|

|

113

|

Thu Apr 17 17:24:58 2025 |

Entered by Nicolas Delerue from 134.158.195.142 on Thu Apr 17 17:24:43 2025 | | Info | Timing |

|

Routage 16,7MHz pour camera a balayage | |

Baie 9: B14 =>cable 94545 => baie 34 A5 |

|

112

|

Thu Apr 17 16:54:51 2025 |

Entered by Nicolas Delerue from 134.158.195.142 on Thu Apr 17 16:54:35 2025 | | Info | Timing |

|

Routage 500MHz anneau pour camera a balayage | |

Le 500MHz pour la camera a balayage est injecte sur la voie C9 dans la baie 09, passe par le cable 90542 et arrive sur la voie A4.

Pour l'instant le 500MHz est pris a la place du scope de la baie 9. |

|

111

|

Wed Mar 12 17:26:49 2025 |

Entered by Nicolas Delerue from 80.119.21.73 on Wed Feb 19 13:59:11 2025 | | Problem | Timing |

|

RE: RE: Probl�me avec le DS SIM/SY/DEG.sim | |

Changement de DS effectué en accord avec la salle de contrôle. Problème résolu, cependant les DS ont mis beaucoup de temps à se charger.

| Entered by Nicolas Delerue from 80.119.21.73 on Wed Feb 19 13:59:11 2025 wrote: |

|

$ ls /data/shared/tangoscripts/DeviceServer/Calibrations/DS/SY

create_ds.sh ds_GeneRetard2_int.py ds_GeneRetard.py launch_ds_Freq.sh loop_create_ds.py

DS_GeneRetard ds_GeneRetard2.py fill_GeneRetard.py launch_ds_gene_retard_loc.sh

DS_GeneRetard2 ds_GeneRetard_float.py Freq launch_ds_gene_retard_new.sh

ds_GeneRetard2_float.py ds_GeneRetard_int.py Freq.py launch_ds_gene_retard.sh

On voit qu'il existe deux versions de ds_GeneRetard, l'une entière et l'autre flottante.

head -50 DS_GeneRetard montre la version de DS_GeneRetard dans tangoscript est la bonne (dtype=float).

$ cat launch_ds_gene_retard.sh

#!/bin/bash

PYTHON=/usr/bin/python

DIR=/data/shared/DS_CALC/gene_retard

$PYTHON $DIR/ds_GeneRetard.py DS_GENERETARD &

$PYTHON $DIR/ds_GeneRetard2.py DS_GENERETARD2 &

On voit que le script execute la version dans DS_CALC et non la version dans tangoscript.

Sur client5:

$ ps -aux | grep ds_Gene

operate+ 48899 0.0 0.1 1465728 118380 ? Sl Jan09 8:47 /usr/bin/python /data/shared/DS_CALC/gene_retard/ds_GeneRetard.py DS_GENERETARD

operate+ 50690 0.0 0.2 1959808 146012 ? Sl Jan09 44:33 /usr/bin/python /data/shared/tangoscripts/DeviceServer/Calibrations/DS/SY/ds_GeneRetard2.py DS_GENERETAR2

nicolas+ 54085 0.0 0.0 12780 952 pts/1 S+ 14:02 0:00 grep ds_Gene

On voit que la version de ds_GeneRetard.py qui s'execute est celle de /data/shared/DS_CALC/gene_retard/ et non celle de /data/shared/tangoscripts

Il faudrait l'arrêter et lancer la bonne version.

Sur client5 (à faire):

kill -9 48899

ps -aux | grep ds_Gene

cd /data/shared/tangoscripts/DeviceServer/Calibrations/DS/SY

ipython /data/shared/tangoscripts/DeviceServer/Calibrations/DS/SY/ds_GeneRetard.py DS_GENERETARD &

| Entered by Nicolas Delerue from 80.119.21.73 on Wed Feb 19 13:59:11 2025 wrote: |

|

Il y a un problème avec le DS SIM/SY/DEG.sim qui stock des valeurs entières au lieu de valeures décimales.

Le problème peut être caractérisé avec le code ci-dessous:

import PyTango

#We create the proxy

tango_synchro = PyTango.DeviceProxy("SIM/SY/DEG.sim")

#we read and printthe delay array

delay_array=tango_synchro.read_attribute("delay")

print(delay_array)

delay_array_val=delay_array.value

#we check one value and modify it to a non interger value and wrote it

print(delay_array_val[2*25+9])

delay_array_val[2*25+9]=42.5

tango_synchro.write_attribute("delay",delay_array_val)

#and read it again

delay_array_val=tango_synchro.read_attribute("delay").value

print(delay_array_val[2*25+9])

#try again

delay_array_val[2*25+9]=44.5

tango_synchro.write_attribute("delay",delay_array_val)

delay_array_val=tango_synchro.read_attribute("delay").value

print(delay_array_val[2*25+9])

|

|

|

|

110

|

Wed Feb 19 14:01:04 2025 |

Entered by Nicolas Delerue from 80.119.21.73 on Wed Feb 19 13:59:11 2025 | | Problem | Timing |

|

RE: Probl�me avec le DS SIM/SY/DEG.sim | |

$ ls /data/shared/tangoscripts/DeviceServer/Calibrations/DS/SY

create_ds.sh ds_GeneRetard2_int.py ds_GeneRetard.py launch_ds_Freq.sh loop_create_ds.py

DS_GeneRetard ds_GeneRetard2.py fill_GeneRetard.py launch_ds_gene_retard_loc.sh

DS_GeneRetard2 ds_GeneRetard_float.py Freq launch_ds_gene_retard_new.sh

ds_GeneRetard2_float.py ds_GeneRetard_int.py Freq.py launch_ds_gene_retard.sh

On voit qu'il existe deux versions de ds_GeneRetard, l'une entière et l'autre flottante.

head -50 DS_GeneRetard montre la version de DS_GeneRetard dans tangoscript est la bonne (dtype=float).

$ cat launch_ds_gene_retard.sh

#!/bin/bash

PYTHON=/usr/bin/python

DIR=/data/shared/DS_CALC/gene_retard

$PYTHON $DIR/ds_GeneRetard.py DS_GENERETARD &

$PYTHON $DIR/ds_GeneRetard2.py DS_GENERETARD2 &

On voit que le script execute la version dans DS_CALC et non la version dans tangoscript.

Sur client5:

$ ps -aux | grep ds_Gene

operate+ 48899 0.0 0.1 1465728 118380 ? Sl Jan09 8:47 /usr/bin/python /data/shared/DS_CALC/gene_retard/ds_GeneRetard.py DS_GENERETARD

operate+ 50690 0.0 0.2 1959808 146012 ? Sl Jan09 44:33 /usr/bin/python /data/shared/tangoscripts/DeviceServer/Calibrations/DS/SY/ds_GeneRetard2.py DS_GENERETAR2

nicolas+ 54085 0.0 0.0 12780 952 pts/1 S+ 14:02 0:00 grep ds_Gene

On voit que la version de ds_GeneRetard.py qui s'execute est celle de /data/shared/DS_CALC/gene_retard/ et non celle de /data/shared/tangoscripts

Il faudrait l'arrêter et lancer la bonne version.

Sur client5 (à faire):

kill -9 48899

ps -aux | grep ds_Gene

cd /data/shared/tangoscripts/DeviceServer/Calibrations/DS/SY

ipython /data/shared/tangoscripts/DeviceServer/Calibrations/DS/SY/ds_GeneRetard.py DS_GENERETARD &

| Entered by Nicolas Delerue from 80.119.21.73 on Wed Feb 19 13:59:11 2025 wrote: |

|

Il y a un problème avec le DS SIM/SY/DEG.sim qui stock des valeurs entières au lieu de valeures décimales.

Le problème peut être caractérisé avec le code ci-dessous:

import PyTango

#We create the proxy

tango_synchro = PyTango.DeviceProxy("SIM/SY/DEG.sim")

#we read and printthe delay array

delay_array=tango_synchro.read_attribute("delay")

print(delay_array)

delay_array_val=delay_array.value

#we check one value and modify it to a non interger value and wrote it

print(delay_array_val[2*25+9])

delay_array_val[2*25+9]=42.5

tango_synchro.write_attribute("delay",delay_array_val)

#and read it again

delay_array_val=tango_synchro.read_attribute("delay").value

print(delay_array_val[2*25+9])

#try again

delay_array_val[2*25+9]=44.5

tango_synchro.write_attribute("delay",delay_array_val)

delay_array_val=tango_synchro.read_attribute("delay").value

print(delay_array_val[2*25+9])

|

|

|

109

|

Wed Feb 19 13:59:26 2025 |

Entered by Nicolas Delerue from 80.119.21.73 on Wed Feb 19 13:59:11 2025 | | Problem | Timing |

|

Probl�me avec le DS SIM/SY/DEG.sim | |

Il y a un problème avec le DS SIM/SY/DEG.sim qui stock des valeurs entières au lieu de valeures décimales.

Le problème peut être caractérisé avec le code ci-dessous:

import PyTango

#We create the proxy

tango_synchro = PyTango.DeviceProxy("SIM/SY/DEG.sim")

#we read and printthe delay array

delay_array=tango_synchro.read_attribute("delay")

print(delay_array)

delay_array_val=delay_array.value

#we check one value and modify it to a non interger value and wrote it

print(delay_array_val[2*25+9])

delay_array_val[2*25+9]=42.5

tango_synchro.write_attribute("delay",delay_array_val)

#and read it again

delay_array_val=tango_synchro.read_attribute("delay").value

print(delay_array_val[2*25+9])

#try again

delay_array_val[2*25+9]=44.5

tango_synchro.write_attribute("delay",delay_array_val)

delay_array_val=tango_synchro.read_attribute("delay").value

print(delay_array_val[2*25+9]) |

|

108

|

Wed Feb 19 10:59:16 2025 |

Entered by Super Team from 134.158.195.141 on Wed Feb 19 10:59:02 2025 | Fixed | Fix | Timing |

|

Carte synchro | |

Changement de carte synchro

le MCT2 de la carte en place à bruler

|

|

107

|

Thu Jan 9 14:12:45 2025 |

Entered by Nicolas Delerue from 134.158.195.144 on Thu Jan 9 14:12:31 2025 | Fixed | Info | Timing |

|

DS to monitor missed triggers | |

A ds to monitor missed triggers has been added in CALC/SY/missed_triggers

|

| Attachment 1: Screenshot_from_2025-01-09_14-24-06.png

|

|

|

106

|

Fri Dec 20 12:03:29 2024 |

Entered by Nicolas Delerue from 134.158.195.142 on Fri Dec 20 12:03:15 2024 | Fixed | Fix | Timing |

|

Added a "diags only" button on Rep rate GUI | |

Two buttons have been added to the repetition rate interface (see attached screen shot):

- "diags only": Will inhibit all channels from the ring and linac delay generators

- "restore linac and ring": Will set all channels of the ring and linac delay generators to External triggering.

A git pull has been done. |

| Attachment 1: Screenshot_from_2024-12-20_12-03-09.png

|

|

| Attachment 2: 20241220_115912.jpg

|

|

| Attachment 3: 20241220_115919.jpg

|

|

|

105

|

Thu Dec 5 15:14:38 2024 |

VC | Fixed | Info | Tests |

|

MESURE STABILIT� SYNCHRO | |

La synchronisation des signaux mesure suR le timing 50Hz

500MHz LI 500MHz RI => 18ps sdev

500MHz LI 50Hz => 190ps sdev

|

|

104

|

Wed Dec 4 11:10:38 2024 |

VC | Fixed | Info | Timing |

|

procedure fr�quence | |

dossier panneau\synchro (cdi)

./ring_frequency.py --help (voir le mode de fonctionnement)

./ring_frequency.py --freq "value" (choisi que des fréquences possible pour la div par 15)

./phase_shifter_rigol.py --phase "value" (attention change les phases de ch1 et ch2) |

|

103

|

Thu Sep 12 09:23:09 2024 |

VC,ND | Fixed | Info | Timing |

|

Decalage temps de declenchement machine. | |

9:20 Le laser est a -8.20us

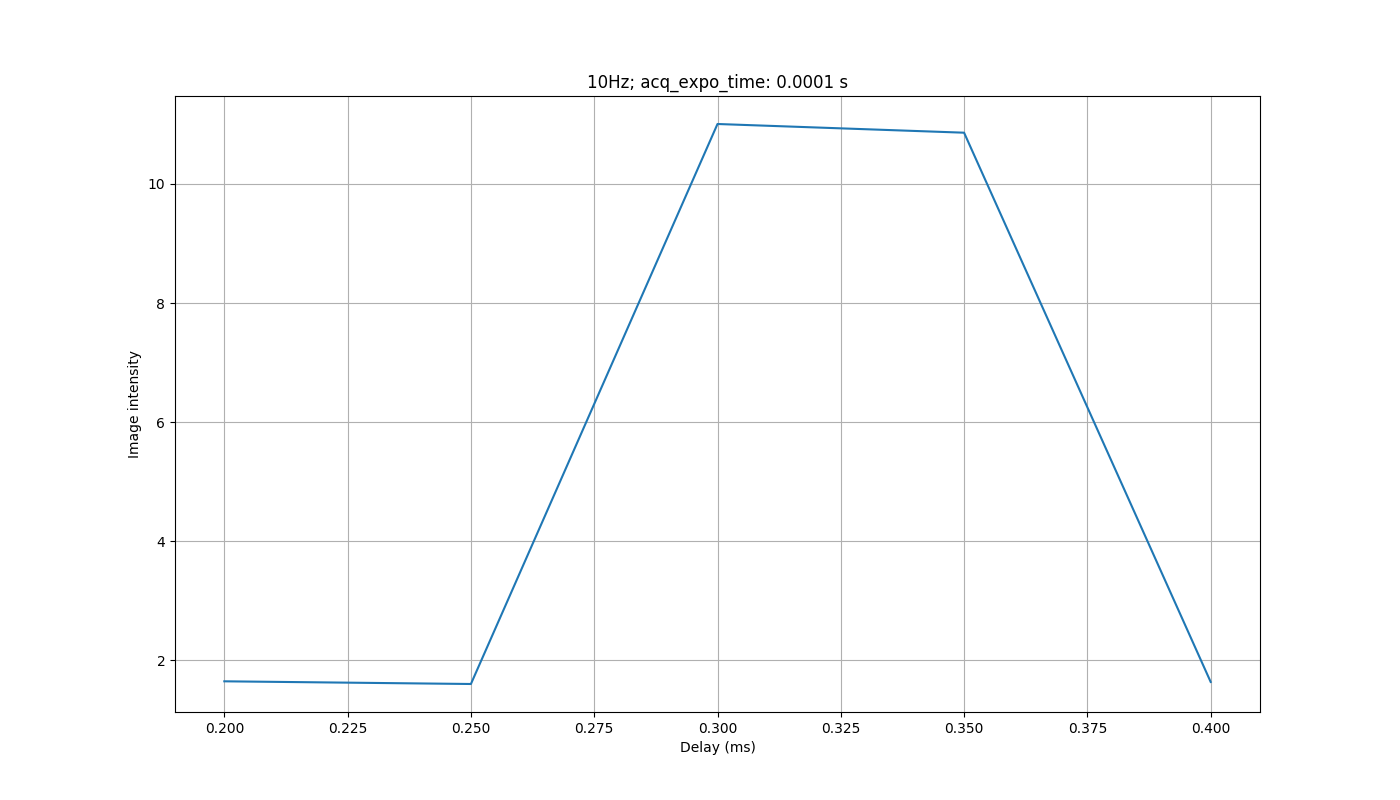

Verification du retard de la camera LI/OP/LAS.02 en decalant en temps le laser de 999us.

La camera se declenche bien environs 600us avant le laser.

Tests sous pylon: un retard de 500us avait ete mis manuellement dans la camera il est retire.

Maintenant la camera se declenche 120us avant le laser.

12:17 Decalage en temps de toutes la synchro. Maintenant le 0 est 200us avant la production des electrons.

Cela devrait etre transparent pour les utilisateurs.

Mise a jour du fichier de constantes de synchronisation.

Git pull.

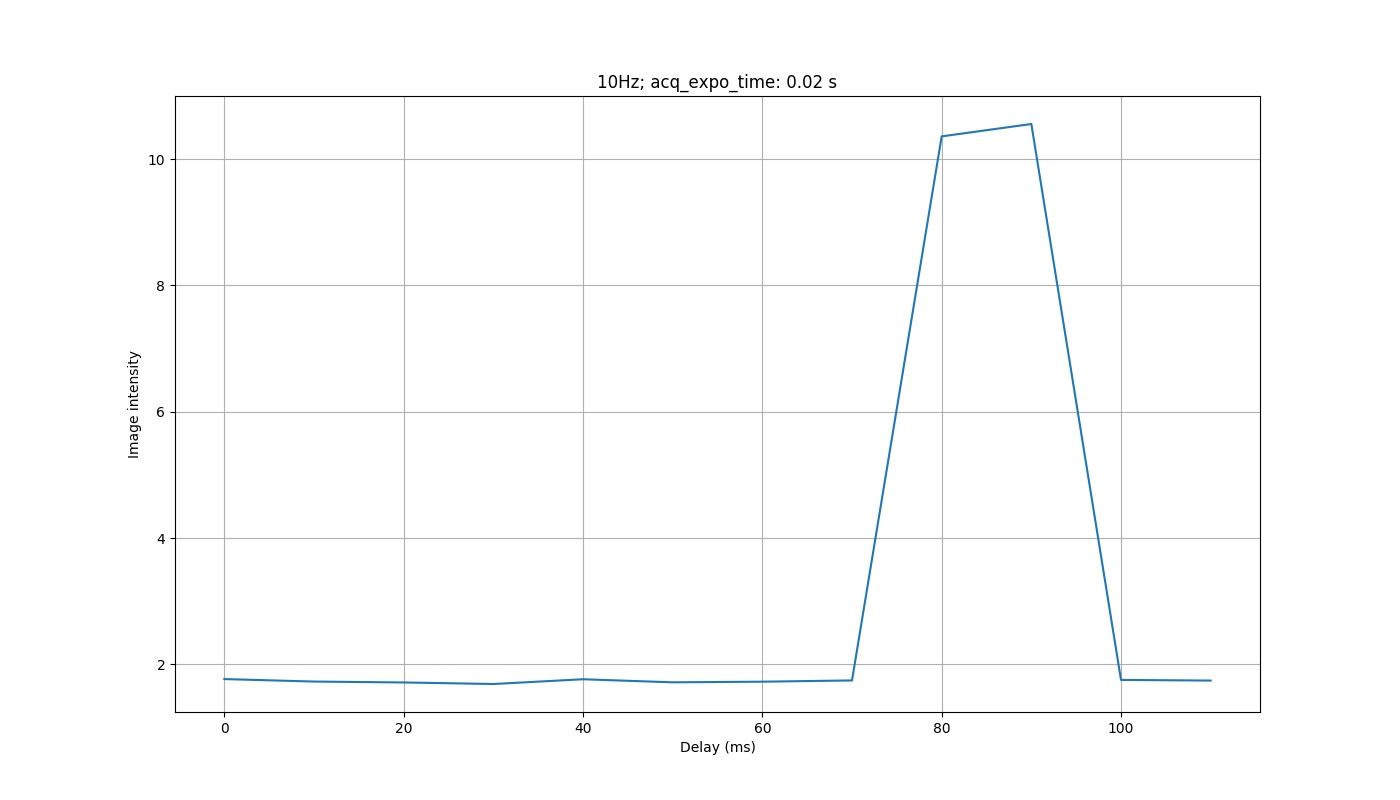

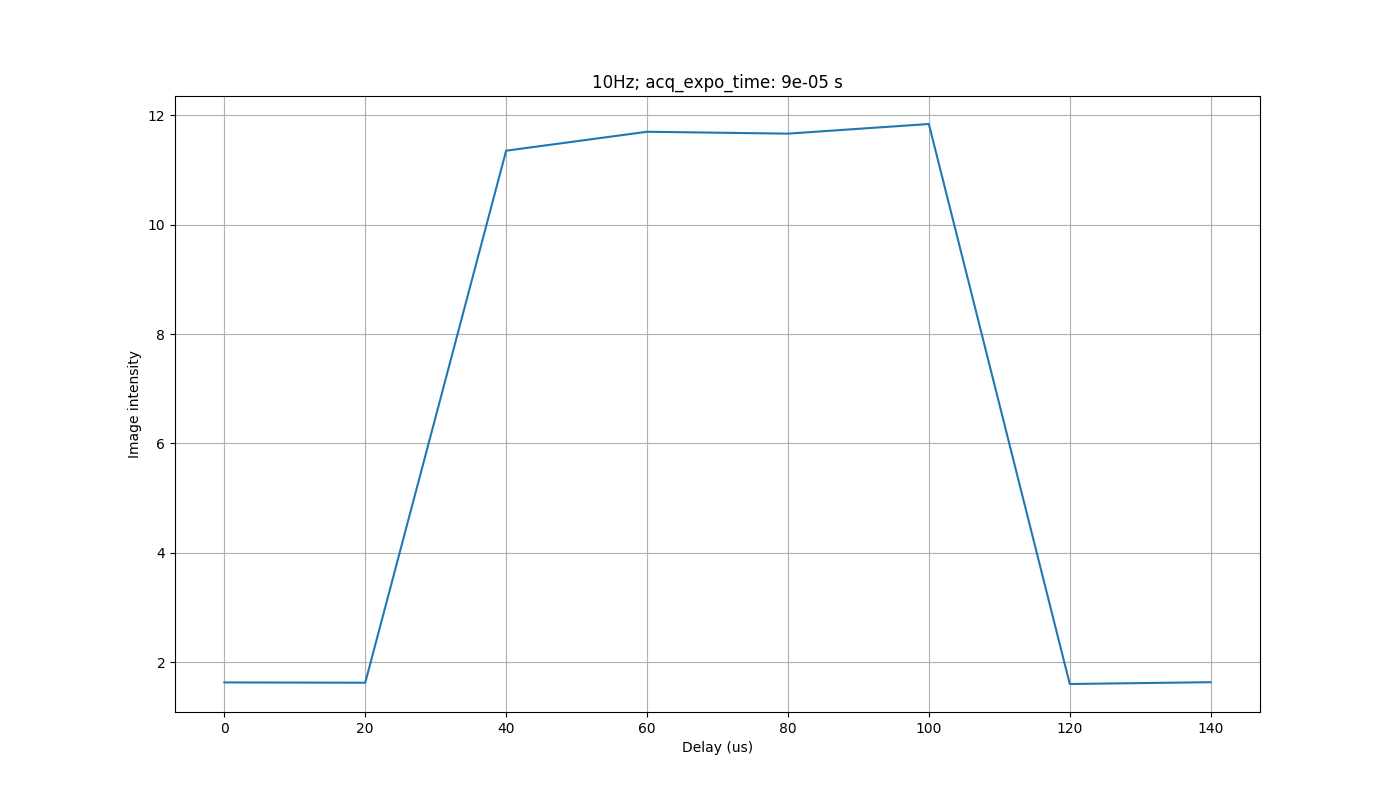

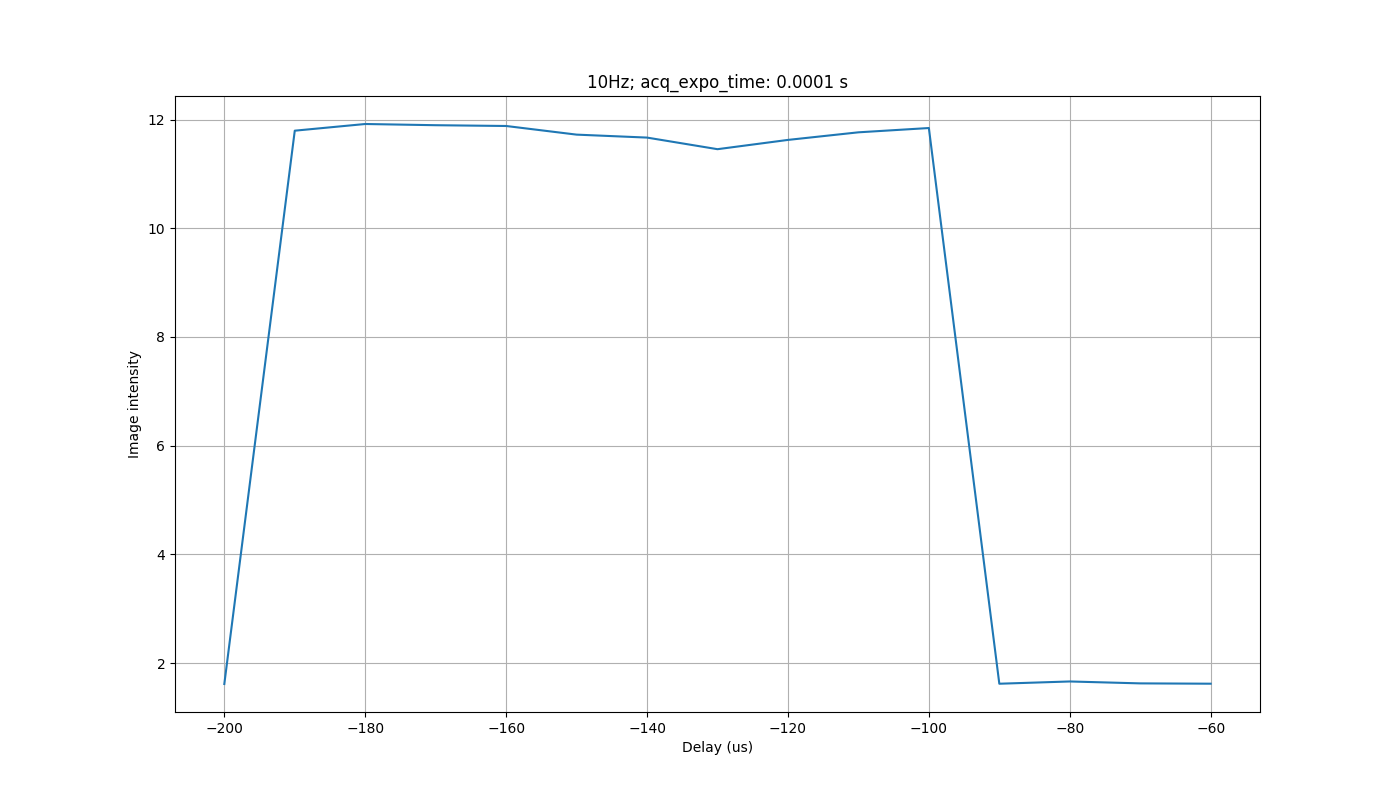

Scan de verification avec le laser a -8.20us et le temps d'exposition de la camera a 100us. On voit bien le laser si le declenechement est entre -190us et -100us

Verification des parametres pylon des autres cameras. A priori il n'y a pas de retard caché.

Il faudra verifier en faisceau que tout va bien.

|

| Attachment 1: laser_scan_before.png

|

|

| Attachment 2: camera_laser_scan_laser_at_999us_exp100us.png

|

|

| Attachment 3: camera_laser_scan_laser_at_200us_exp90us_after_changing_edge.png

|

|

| Attachment 4: camera_laser_scan_laser_at_m8us_exp100us_after_adjusting_timing.png

|

|

|

102

|

Tue Jul 16 13:00:24 2024 |

VC, ND | Fixed | Info | Timing |

|

RE: Codes de synchro mis a jour (25Hz) | |

La limite sur les diags a levee. Ils peuvent passer a 25Hz aussi.

| VC, ND wrote: |

|

Les codes de synchro ont ete mis a jour et testes.

Il est maintannt possible de passer a 25Hz sur le linac et l'anneau. Les diags sont limites a 8,33Hz.

|

|

|

101

|

Tue Jul 16 11:47:44 2024 |

VC, ND | Fixed | Info | Material |

|

RE: Synthe linac | |

Attention si vous passez pres de la baie 8: certains cables n'aiment pas etre caresse. Si le voyant trigger ne clignote plus, appelez la synchro...

| VC, ND wrote: |

|

Le synthe du linac a ete remis en place et teste a bas niveau.

|

|

|

100

|

Tue Jul 16 11:20:49 2024 |

VC, ND | Fixed | Info | Material |

|

Synthe linac | |

Le synthe du linac a ete remis en place et teste a bas niveau. |

|

99

|

Tue Jul 16 11:07:39 2024 |

VC, ND | Fixed | Info | Timing |

|

Codes de synchro mis a jour (25Hz) | |

Les codes de synchro ont ete mis a jour et testes.

Il est maintannt possible de passer a 25Hz sur le linac et l'anneau. Les diags sont limites a 8,33Hz. |