L'ajout du 16MHz anneau est nécessaire pour la synchro.

La modif est effectuée dans le chassis TriggerBox (baie 8) => sur la carte CPLD l'entrée IN2 (initialement mélange 3GHz linac - 125MHz ring) devient le 16MHz ring

la connection entre la baie 9 et la baie 8utilise le cable 90359 Baie9-D2 Baie-E8 (anciennement 10MHz

Résultats:

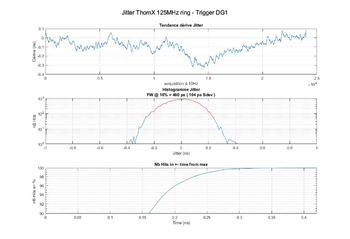

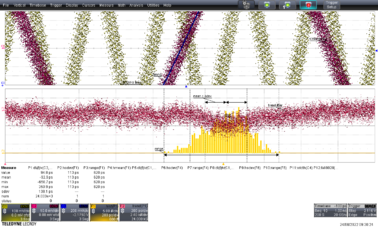

mesure effectuée entre le 125MHz anneau et une voie de timing du DG1

sur 1mn le jitter entre les signaux RF (500MHz ring 3GHz anneau et leurs sous-multiples) est de l'ordre de 110ps Sdev

sur 40mn la largeur à 1% est inférieure à 600ps et la dérive de la valeur moyenne est de l'ordre de 300ps

l'ensemble des données est contenu dans un jitter inférieur à 1ns

|